l對于正弦信號,流過一個元器件的電流和其兩頭的電壓,它們的相位不一定是雷同的。這類相位差是若何發生的呢?這類常識異常重要,由于不只放大器、自激振蕩器的反應信號要斟酌相位,并且在結構一個電路時也必要充足懂得、利用或防止這類相位差。上面探究這個成績。

起首,要懂得一下一些元件是若何構建進去的;其次,要懂得電路元器件的根本事情事理;第三,據此找到懂得相位差發生的緣故原由;第四,利用元件的相位差特征結構一些根本電路。

一、電阻、電感、電容的產生進程

科學家顛末歷久的察看、實驗,弄清楚了一些事理,也常常呈現了一些預料之外的偶爾發明,如倫琴發明X射線、居里夫人發明鐳的輻射征象,這些偶爾的發明竟然成為了偉大的迷信成績。電子學范疇也是如斯。

科學家讓電流流過導線的時刻,偶爾發清楚明了導線發燒、電磁感到征象,進而發清楚明了電阻、電感。迷信家還從磨擦起電征象獲得靈感,發清楚明了電容。發明整流征象而創造出二極管也是偶爾。

二、元器件的根本事情事理

電阻——電能→熱能

電感——電能→磁場能,&磁場能→電能

電容——電勢能→電場能,&電場能→電流

因而可知,電阻、電感、電容便是動力轉換的元件。電阻、電感完成不同種類能量間的轉換,電容則完成電勢能與電場能的轉換。

1 電阻

電阻的事理是:電勢能→電流→熱能。

電源正負兩頭貯藏有電勢能(正負電荷),當電勢加在電阻兩頭,電荷在電勢差感化下活動——構成為了電流,其活動速率遠比無電勢差時的亂序自在活動快,在電阻或導體內碰撞發生的熱量也就更多。

正電荷從電勢高的一端進入電阻,負電荷從電勢低的一端進入電阻,兩者在電阻內部停止中和感化。中和感化使得正電荷數目在電阻內部呈現從高電勢端到低電勢端的梯度散布,負電荷數目在電阻內部呈現從低電勢端到高電勢端的梯度散布,從而在電阻兩頭發生了電勢差,這便是電阻的電壓降。異樣電流下,電阻對中和感化的阻力越大,其兩頭電壓降也越大。

是以,用R=V/I來權衡線性電阻(電壓降與經由過程的電流成正比)的阻力巨細。

對交換旌旗燈號則表白為R=v(t)/i(t)。

留意,也有非線性電阻的觀點,其非線性有電壓影響型、電流影響型等。

2 電感

電感的事理:電感——電勢能→電流→磁場能,&磁場能→電勢能(若有負載,則→電流)。

當電源電勢加在電感線圈兩頭,電荷在電勢差感化下活動——構成為了電流,電流轉變磁場,這稱為“充磁”進程。若被充磁電感線圈兩頭的電源電勢差撤消,且電感線圈外接有負載,則磁場能在衰減的進程中轉換為電能(如負載為電容,則為電場能;若負載為電阻,則為電流),這稱為“去磁”進程。

權衡電感線圈充磁多少的單元是磁鏈——Ψ。電流越大,電感線圈被沖磁鏈就越多,即磁鏈與電流成正比,即Ψ=L*I。對一個指定電感線圈,L是常量。

是以,用L=Ψ/I表白電感線圈的電磁轉換才能,稱L為電感量。

電感量的微分表白式為:L=dΨ(t)/di(t)。

依據電磁感到事理,磁鏈變更發生感到電壓,磁鏈變更越大則感到電壓越高,即v(t)=d dΨ(t)/dt。

綜合上面兩公式獲得:v(t)=L*di(t)/dt,即電感的感到電壓與電流的變更率(對時間的導數)成正比,電流變更越快則感到電壓越高。

3 電容

電容的事理:電勢能→電流→電場能,電場能→電流。

當電源電勢加在電容的兩個金屬極板上,正負電荷在電勢差感化下分離向電容兩個極板湊集而構成電場,這稱為“充電”進程。若被充電電容兩頭的電源電勢差撤消,且電容外接有負載,則電容兩頭的電荷在其電勢差下向外流走,這稱為“放電”進程。電荷在向電容湊集和從電容兩個極板向外流走的進程中,電荷的活動就構成為了電流。

要分外留意,電容上的電流并非電荷真的流過電容兩個極板間的絕緣介質,而只是充電進程中電荷從內部向電容兩個極板湊集構成的活動,和放電進程中電荷從電容兩個極板向外流走而構成的活動。也便是說,電容的電流其實是內部電流,而非內部電流,這與電阻、電感都不異樣。

權衡電容充電多少的單元是電荷數——Q。電容極板間電勢差越大,闡明電容極板被沖電荷越多,即電荷數與電勢差(電壓)成正比,即Q=C*V。對指定電容,C是常量。

是以,用C=Q/V表白電容極板儲存電荷的才能,稱C為電容量。

電容量的微分表白式為:C=dQ(t)/dv(t)。

由于電流即是單元時間內電荷數的變更量,即i(t)=dQ(t)/dt,

綜合上面兩個公式獲得:i(t)=C*dv(t)/dt,即電容電流與其上電壓的變更率(對時間的導數)成正比,電壓變更越快則電流越大。

小結:

v(t)=L*di(t)/dt注解電流變更構成為了電感的感到電壓(電流穩定則沒有感到電壓構成)。

i(t)=C*dv(t)/dt注解電壓變更構成為了電容的內部電流(現實是電荷量變更。電壓穩定則沒有電容的內部電流構成)。

三、元件對信號相位的轉變

起首要提示,相位的觀點是針對正弦信號而言的,直流信號、非周期變更信號等都沒有相位的觀點。

1 電阻上的電壓電流同相位

由于電阻上電壓v(t)=R*i(t),若i(t)=sin(ωt+θ),則v(t)=R* sin(ωt+θ)。

以是,電阻上電壓與電流同相位。

2 電感上的電流后進電壓90°相位

由于電感上感到電壓v(t)=L*di(t)/dt,若i(t)=sin(ωt+θ),則v(t)=L*cos(ωt+θ)。

以是,電感上電流后進感到電壓90°相位,或者說感到電壓超前電流90°相位。

直觀懂得:假想一個電感與電阻串連充磁。從充磁進程看,充磁電流的變更惹起磁鏈的變更,而磁鏈的變更又發生感到電動勢和感到電流。依據楞次定律,感到電流偏向與充磁電流相同,延緩了充磁電流的變更,使得充磁電流相位后進于感到電壓。

3 電容上的電流超前電壓90°相位

由于電容上電流i(t)=C*dv(t)/dt,若v(t)=sin(ωt+θ),則i(t)=L*cos(ωt+θ)。

以是,電容上電流超前電壓90°相位,或者說電壓后進電流90°相位。

直觀懂得:假想一個電容與電阻串連充電。從充電進程看,老是先有活動電荷(即電流)的積聚才有電容上的電壓變更,即電流老是超前于電壓,或者說電壓老是后進與電流。上面的積分方程能表現這類直觀性:

v(t)=(1/C)*∫i(t)*dt=(1/C)*∫dQ(t),即電荷變更的積聚構成為了電壓,故dQ(t)相位超前v(t);而電荷積聚的進程便是電流同步變更的進程,即i(t)與dQ(t)同相。是以i(t)相位超前于v(t)。

四、元件相位差的利用——RC文氏橋、LC諧振進程的懂得

不管RC文氏橋,照樣LC的串連諧振、并聯諧振,都是由電容或/和電感容元件的電壓、電流相位差惹起的,就像機器共振的節奏異樣。

當兩個頻率雷同、相位相位的正弦波疊加時,疊加波的幅度到達最大值,這便是共振征象,在電路里稱為諧振。

兩個頻率雷同、相位相同的正弦波疊加,疊加波的幅度會降到最低,乃至為零。這便是減小或接收振動的事理,如降噪裝備。

當一個體系中有多個頻率旌旗燈號混應時,假如有兩個同頻旌旗燈號發生了共振,那末這個體系中別的振動頻率的能量就被這兩個同頻、同相的旌旗燈號所接收,從而起到了對別的頻率的過濾感化。這便是電路中諧振過濾的事理。

諧振必要同時滿意頻率雷同和相位雷同兩個前提。電路若何經由過程幅度-頻率特征抉擇頻率的辦法曩昔在RC文氏橋中講過,LC串并聯的思緒與RC雷同,這里再也不贅述。上面咱們來看看電路諧振中相位賠償的大略估量(更準確的相位偏移則要盤算)。

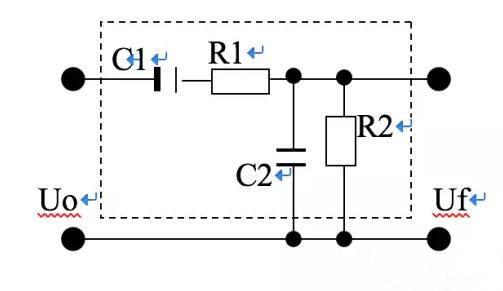

1 RC文氏橋的諧振(圖1)

若沒有C2,正弦信號Uo的電流由C1→R1→R2,通過R2上壓降形成Uf輸出電壓。由于支路電流被電容C1移相超前Uo 90°,這超前相位的電流流過R2(電阻不產生相移!),使得輸出電壓Uf電壓超前于Uo 90°。

在R2上并聯C2,C2從R2取得電壓,由于電容對電壓的滯后作用,使得R2上電壓也被強制滯后。(但不一定有90°,因為還有C1→R1→C2電流對C2上電壓即Uf的影響,但在RC特征頻率上,并聯C2后Uf輸出相位與Uo相同。)

小結:并聯電容使得電壓信號相位滯后,稱為電壓相位的并聯補償。

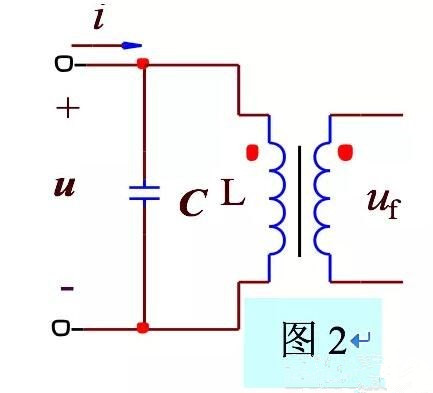

2 LC并聯諧振(圖2)

若沒有電容C,正弦信號u通過L感應到次級輸出Uf,Uf電壓超前于u 90°;

在L初級并聯電容C,由于電容對電壓的滯后作用,使得L上電壓也被強制滯后90°。因此,并聯C后Uf輸出相位與u相同。

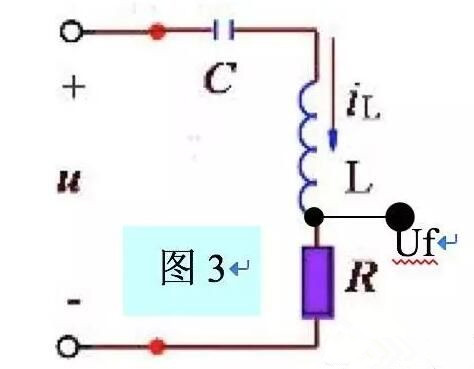

3 LC串聯諧振(圖3)

對于輸入正弦信號u,電容C使得串聯回路中負載R上的電流相位超前于u 90°,電感L則使得同一串聯回路中的電流相位再滯后90°二者相位偏移剛好抵消。因此,輸出Uf與輸入u同相。

總結:(注意,相位影響不一定都是90°,與其它部分相關,具體則要計算)

串聯電容使得串聯支路電流相位超前,從而影響輸出電壓相位。

并聯電容使得并聯支路電壓相位滯后,從而影響輸出電壓相位。

串聯電感使得串聯支路電流相位滯后,從而影響輸出電壓相位。

并聯電感使得并聯支路支路電壓超前,從而影響輸出電壓相位。